fpga开发

FPGA开发:重塑硬件设计的灵活性与创新

FPGA开发:重塑硬件设计的灵活性与创新

引言

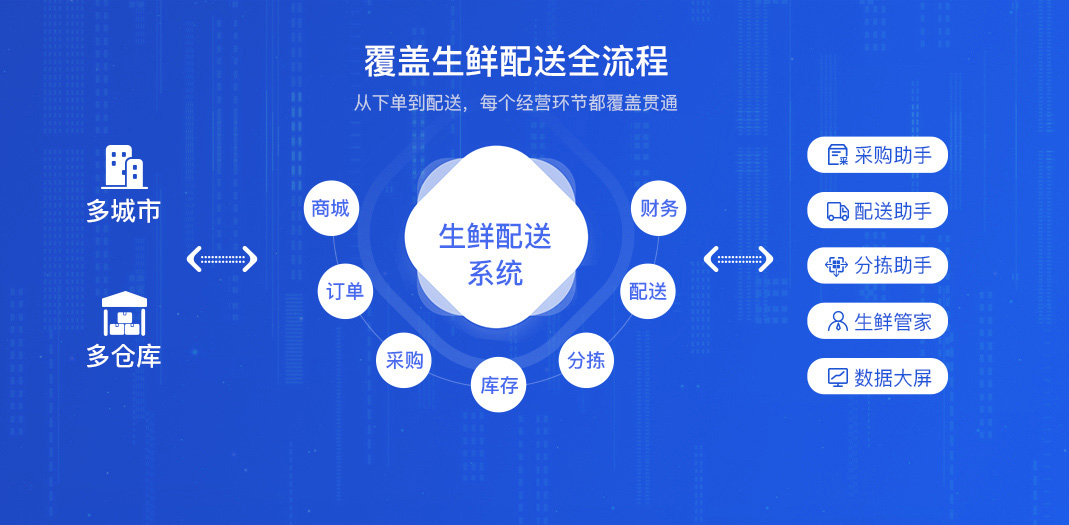

在数字化浪潮的推动下,硬件设计领域正经历一场静默的革命。现场可编程门阵列(Field-Programmable Gate Array, FPGA)凭借其独特的可重构特性,成为连接软件灵活性与硬件高效性的桥梁。不同于传统固定功能的芯片,FPGA允许工程师通过编程重新定义硬件逻辑,为5G通信、人工智能、工业自动化等领域提供了前所未有的可能性。

一、FPGA的核心优势

1. 硬件可重构性

FPGA由大量可编程逻辑单元、存储模块和互连资源构成,支持用户通过硬件描述语言(如Verilog或VHDL)动态配置电路功能。这种特性使得单一芯片能适应多种应用场景,例如:通信基站可通过FPGA动态切换4G/5G协议,自动驾驶系统能实时更新传感器处理算法。

2. 并行计算能力

与CPU顺序执行指令不同,FPGA可同时激活数百万逻辑单元,特别适合需要高吞吐量的任务。在金融高频交易中,FPGA的微秒级延迟远超GPU;在图像处理领域,其像素级并行架构可实时处理8K视频流。

3. 能效比突破

通过定制化数据路径设计,FPGA可消除通用处理器中的冗余指令开销。微软Azure智能网卡采用FPGA卸载网络协议栈,使服务器CPU负载降低40%,整体能效提升达30%。

二、FPGA开发全流程解析

1. 系统架构设计

开发者需在算法优化与硬件资源间取得平衡。例如,卷积神经网络加速需权衡乘法器数量与内存带宽,通常采用Winograd算法减少70%的乘加操作。

2. 硬件描述与仿真

使用SystemVerilog编写模块时,同步设计原则至关重要。高级综合工具(HLS)可将C++代码转换为RTL,但需通过co-simulation验证功能正确性。某医疗影像团队通过QuestaSim发现时序违例,避免了批量生产后的召回风险。

3. 布局布线优化

Xilinx Vivado的PhysOpt技术可自动优化关键路径时序。实际案例显示,对DDR4接口模块实施区域约束,能使时序裕量提升15%,功耗降低8%。

4. 在线调试与迭代

ChipScope和SignalTap等工具支持实时信号抓取。某汽车电子厂商通过JTAG在线调试,3小时内定位了CAN总线数据丢包问题,较传统示波器检测效率提升10倍。

三、行业应用与挑战

1. 前沿领域实践

– 云计算:AWS F1实例允许用户快速部署定制化加速器,某基因组公司实现DNA比对速度提升220倍。

– 边缘AI:莱迪思SensAI方案在2W功耗下实现实时人脸识别,延迟小于10ms。

– 自动驾驶:特斯拉采用FPGA实现传感器融合预处理,将数据带宽需求降低60%。

2. 开发痛点与对策

– 时序收敛难题:采用增量编译策略,保留已验证模块布局,某5G项目开发周期缩短40%。

– 功耗管理:使用动态电压频率缩放(DVFS),英特尔Stratix 10在空闲时段可降低50%功耗。

– 人才短缺:Xilinx与高校合作推出Vitis开发认证,全球已有超5万名工程师通过考核。

四、未来趋势与生态演进

1. 异构计算融合

AMD Xilinx Versal系列将ARM核、AI引擎与FPGA整合,在机器视觉任务中展现10倍于GPU的能效比。OpenCL和OneAPI标准正在打破软硬件生态壁垒。

2. 开发范式革新

高层次综合(HLS)工具支持从Python直接生成电路,Google团队已实现用TensorFlow语法开发TPU类加速器。AI驱动的布局工具(如Cadence Cerebrus)可将工程效率提升5倍。

3. 云原生FPGA服务

微软Azure提供FPGA即服务(FaaS),开发者可远程调用赛灵思Alveo加速卡资源,某区块链公司借此将智能合约验证成本降低80%。

结语

FPGA正在从传统的原型验证工具进化为智能系统的核心引擎。随着3D堆叠、光互连等技术的发展,未来FPGA的容量和带宽将呈现指数级增长。开发者需要持续更新跨学科知识储备,在软件定义硬件的时代,掌握FPGA技术意味着掌握了重塑物理世界与数字世界边界的钥匙。

点击右侧按钮,了解更多行业解决方案。

相关推荐

fpga开发是什么意思

fpga开发是什么意思

FPGA开发是指基于现场可编程门阵列(Field-Programmable Gate Array,FPGA)技术进行硬件电路设计与实现的过程。作为一种半定制化的集成电路,FPGA凭借其可重复编程和高并行处理能力,在通信、人工智能、工业控制等领域展现出独特优势。以下从核心概念、开发流程和应用场景三个维度展开解析。

一、FPGA技术原理

FPGA芯片由可编程逻辑单元(CLB)、互连资源(Interconnect)和输入输出模块(IOB)构成矩阵式架构。每个逻辑单元包含查找表(LUT)和触发器,通过烧录配置文件实现硬件功能的动态重构。这种特性使其区别于ASIC固定电路结构,开发者无需流片即可完成功能验证。

硬件描述语言(HDL)是开发的核心工具,Verilog和VHDL作为行业标准语言,通过行为级、RTL级描述实现数字逻辑设计。现代高阶综合工具(HLS)支持C++/Python直接转换为硬件电路,开发效率提升显著。例如Xilinx Vivado HLS可将算法代码自动优化为并行化硬件模块。

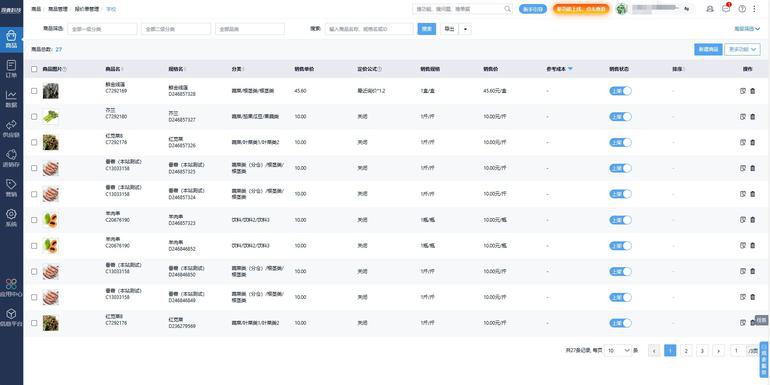

二、开发流程解析

典型开发流程包含需求分析、架构设计、功能仿真、综合实现和板级调试五个阶段。设计输入阶段需权衡时序约束与资源利用率,采用模块化设计提升复用性。综合过程将HDL代码映射为门级网表,布局布线工具根据时序要求优化逻辑单元布局。

时序收敛是开发难点,需通过约束文件设定时钟频率,利用时序分析工具排查关键路径。功耗优化涉及时钟门控、数据路径优化等技术。调试阶段常使用ChipScope等在线逻辑分析仪,通过插入探针实时捕获信号状态。某5G基站项目开发中,团队通过流水线优化将数据处理延迟降低42%。

三、行业应用实践

在通信领域,FPGA广泛用于基站波束成形和协议加速。某运营商采用Virtex UltraScale+实现5G NR物理层,处理时延较DSP方案降低60%。工业场景中,多轴运动控制器通过FPGA实现微秒级同步控制,某数控机床厂商借此将加工精度提升至0.1μm。

人工智能推理加速是新兴方向,通过定制化卷积运算单元,ResNet50推理速度可达GPU的3倍功耗仅1/5。航空航天领域,星载计算机利用FPGA的抗辐射特性,某遥感卫星实现星上实时图像压缩,数据回传效率提升70%。

FPGA开发正朝着异构计算方向发展,Zynq UltraScale+等SoC器件集成ARM核与可编程逻辑,支持软硬协同设计。随着国产化进程加速,紫光同创等厂商的28nm器件已实现进口替代。开发者需持续跟进OpenCL开发框架、部分可重构(Partial Reconfiguration)等新技术,在性能与灵活性间取得最优平衡。

点击右侧按钮,了解更多行业解决方案。

fpga开发平台有哪些

fpga开发平台有哪些

FPGA(现场可编程门阵列)开发平台是电子系统设计的重要工具,涵盖硬件开发板、软件工具链及生态系统支持。以下是主流FPGA开发平台的综合介绍,帮助开发者根据需求选择合适方案。

一、Xilinx(AMD)平台

作为FPGA行业龙头,Xilinx提供全系列产品线:

- 硬件开发板:

- 高端:Virtex系列的VCU118、KCU105,支持高速接口(PCIe Gen4、100G以太网),适用于数据中心和通信。

- 中端:Kintex系列的KC705,适合工业控制与视频处理。

- 低成本:Artix-7的Basys3和Nexys4 DDR,面向学生和入门开发者。

- 软件工具:

- Vivado Design Suite:集成综合、布局布线、调试功能,支持RTL级设计。

- Vitis Unified Software Platform:支持C/C++/OpenCL的高层次合成(HLS),加速算法开发。

- 生态系统:提供丰富的IP核库(如视频编解码器)、AWS云FPGA实例,以及Pynq框架实现Python编程。

二、Intel(原Altera)平台

Intel FPGA以高性能和异构计算为特色:

- 硬件开发板:

- Stratix 10 GX FPGA开发套件:针对AI加速和高速网络(56G收发器)。

- DE10-Nano:集成双核ARM处理器,适合嵌入式SoC开发。

- Cyclone V系列:成本敏感型应用(如DE0-Nano)。

- 软件工具:

- Quartus Prime:支持全流程设计,与ModelSim深度集成仿真。

- Intel oneAPI:支持跨CPU/GPU/FPGA的统一编程。

- 应用场景:5G基带处理、自动驾驶实时计算。

三、Lattice Semiconductor平台

以低功耗和小封装见长,适合边缘计算:

- 产品系列:

- iCE40 UltraPlus:功耗低至1mW,用于IoT传感器。

- ECP5:12G SerDes接口,适合工业自动化。

- 开发工具:

- Lattice Radiant:针对中端FPGA的轻量化工具。

- 开源支持:Yosys+NextPnR工具链可替代厂商软件,降低授权成本。

- 典型开发板:iCE40 HX8K(10美元级)、CrossLink-NX视频处理板。

四、Microchip(Microsemi)平台

聚焦高可靠性与安全性:

- 硬件平台:

- PolarFire系列:唯一支持抗辐射的民用级FPGA,适用于航天与电网。

- SmartFusion2:集成ARM Cortex-M3,用于功能安全系统。

- 开发工具:

- Libero SoC:提供时序约束自动化与安全配置管理。

- SoftConsole:基于Eclipse的嵌入式软件开发环境。

五、第三方开发平台

- Digilent:与Xilinx合作推出Nexys、Arty系列,配备Pmod扩展接口。

- Terasic:提供DE系列开发板(如DE10-Lite),配套教程丰富。

- 开源硬件:如TinyFPGA、IceBreaker,兼容开源工具链。

六、国产FPGA平台

- 紫光同创:Logos/PG系列对标Xilinx 7系,配套PDS开发工具。

- 安路科技:EAGLE系列主打低功耗,支持国产EDA工具。

选择建议

- 初学者:Basys3(Xilinx)或DE10-Nano(Intel),搭配详细教程。

- 高速原型验证:Xilinx VCU118或Intel Stratix 10。

- 边缘AI部署:Lattice CrossLink-NX结合低功耗优势。

- 功能安全场景:Microchip PolarFire系列。

FPGA开发平台的选择需综合评估性能需求、功耗预算、工具链成熟度及社区资源。随着开源工具和国产芯片的崛起,开发者正获得更多灵活选择。

点击右侧按钮,了解更多行业解决方案。

fpga开发流程

fpga开发流程

FPGA(现场可编程门阵列)开发是一种通过硬件描述语言(HDL)实现定制化数字电路设计的技术流程。其开发流程高度系统化,涵盖从需求分析到硬件部署的全生命周期。以下将详细阐述FPGA开发的七大核心步骤,帮助开发者构建高效可靠的硬件系统。

一、需求分析与架构设计

开发初期需明确功能指标(如处理速度、资源占用率)和性能边界条件(功耗限制、接口协议)。基于需求选择合适型号的FPGA芯片,需综合评估逻辑单元数量、存储资源、DSP模块和高速接口等硬件参数。架构设计阶段采用模块化分解策略,通过状态机划分、数据流优化提升系统并行性,例如将图像处理拆分为像素采集、算法核、输出控制等子模块。

二、HDL设计与代码实现

使用Verilog或VHDL进行寄存器传输级(RTL)编码,推荐采用Intel Quartus或Xilinx Vivado开发环境。关键代码规范包括:

- 严格遵循同步设计原则,时钟域交叉处使用双触发器同步

- 有限状态机采用三段式写法增强可读性

- 参数化设计通过`define宏定义提高代码复用率

- 组合逻辑避免锁存器产生,时序逻辑明确复位策略

示例代码片段:

verilog

module FIR_filter(

input clk, rst_n,

input [7:0] data_in,

output reg [15:0] data_out

);

reg [7:0] delay_line [0:3];

always @(posedge clk) begin

if(!rst_n) delay_line <= '{default:0}; else begin delay_line[0] <= data_in; for(int i=1; i<4; i++) delay_line[i] <= delay_line[i-1]; end end endmodule 三、功能仿真验证 搭建SystemVerilog或UVM验证平台进行模块级测试,重点验证: - 边界条件:极值输入、连续突发数据 - 协议符合性:AXI总线时序、握手信号 - 覆盖率指标:语句覆盖、条件覆盖、FSM状态转移 使用ModelSim运行测试用例,通过波形分析工具检查时序关系,典型问题包括信号竞争、未初始化寄存器等。 四、综合与优化 逻辑综合将RTL转换为门级网表,需设置时序约束(SDC文件)和面积约束。优化策略包括: - 关键路径流水线化:插入寄存器平衡逻辑级数 - 资源共享:复用乘法器减少DSP消耗 - 功耗优化:门控时钟技术降低动态功耗 综合报告需重点关注最大频率(Fmax)、资源利用率(LUT/FF占比)等指标。 五、布局布线与时序收敛 布局布线(PAR)阶段进行物理映射,通过增量布局策略改善时序。时序分析需检查建立时间(Setup Time)和保持时间(Hold Time)违例,使用Tcl脚本自动优化跨时钟域路径。当无法满足时序要求时,需返回设计阶段进行架构调整或约束放松。 六、板级调试与验证 使用SignalTap II或ChipScope进行片上调试,通过JTAG接口抓取内部信号。调试重点包括: - 电源完整性:测量纹波噪声不超过芯片规格的5% - 信号完整性:使用眼图分析高速串行链路质量 - 功能验证:白盒测试覆盖所有工作模式 七、系统集成与维护 生成Bitstream配置文件后,通过QSPI闪存固化程序。建立版本控制系统管理不同配置版本,使用自动化脚本实现持续集成。定期进行老化测试,监控高温环境下的时序余量变化。 FPGA开发本质是软硬件协同的迭代过程,据统计,优秀设计需经历3-5次设计迭代,调试时间约占项目周期的40%。掌握标准化开发流程可显著降低设计风险,最新工具链(如Vitis HLS)支持C/C++高层次综合,正在改变传统开发模式。开发者需持续关注异构计算、部分重配置等前沿技术演进。

点击右侧按钮,了解更多行业解决方案。

免责声明

本文内容通过AI工具智能整合而成,仅供参考,e路人不对内容的真实、准确或完整作任何形式的承诺。如有任何问题或意见,您可以通过联系1224598712@qq.com进行反馈,e路人收到您的反馈后将及时答复和处理。